# E0C88348 DEVELOPMENT HARDWARE TOOL E0C88P348 TECHNICAL MANUAL

**E0C88P348 Technical Hardware**

### **P**REFACE

This manual describes the hardware specification of the E0C88P348.

The E0C88P348 is a development tool for the E0C88348. The mask ROM in the E0C88348 has been changed to a Flash EEPROM. Almost all other circuits are compatible with the E0C88348, therefore this manual explains only the parts related to the PROM and other differences from the E0C88348. Furthermore, an exclusive PROM writer (UNIVERSAL ROM WRITER II) should be used for PROM programming.

Refer to the following manuals in addition to this manual.

For the functions and control of the peripheral circuit: "E0C88348 Technical Manual" For the exclusive PROM writer and programming:

"Universal ROM Writer II Hardware Manual"

"E0C88PxxxUniversal ROM Writer II User's Manual"

"E0C88P348 Adapter Socket Hardware Manual"

### **CONTENTS**

| CHAPTER 1 | OU               | TLINE                                                                                                                                                                                     | 1  |

|-----------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|           | 1.1              | Features                                                                                                                                                                                  |    |

|           | 1.2              | Block Diagram                                                                                                                                                                             |    |

|           | 1.3              | Pin Layout Diagram                                                                                                                                                                        |    |

|           | 1.4              | Pin Description                                                                                                                                                                           |    |

| CHAPTER 2 | PR               | OM Programmer and Operating Modes                                                                                                                                                         | 5  |

|           | 2.1              | Configuration of PROM Programmer                                                                                                                                                          |    |

|           | 2.2              | Operating Modes         6           2.2.1 Normal operation mode         6           2.2.2 PROM serial programming mode         6           2.2.3 PROM parallel programming mode         7 |    |

| CHAPTER 3 | DIF              | FERENCES FROM E0C88348                                                                                                                                                                    | 8  |

|           | 3.1              | Terminal Configuration8                                                                                                                                                                   |    |

|           | 3.2              | Mask Option9                                                                                                                                                                              |    |

|           | 3.3              | Power Supply                                                                                                                                                                              |    |

|           | 3.4              | Initial Reset                                                                                                                                                                             |    |

|           | 3.5              | <i>ROM</i>                                                                                                                                                                                |    |

|           | 3.6              | Oscillation Circuit                                                                                                                                                                       |    |

|           | 3.7              | SVD Circuit                                                                                                                                                                               |    |

| CHAPTER 4 | SUN              | MMARY OF NOTES                                                                                                                                                                            | 14 |

|           | 4.1              | Notes Related to the PROM                                                                                                                                                                 |    |

|           | 4.2              | Notes on Differences form the E0C88348                                                                                                                                                    |    |

| CHAPTER 5 | $\mathbf{R}_{A}$ | CIC EVTEDNAL WIDING DIACDAM                                                                                                                                                               | 15 |

| CHAPTER 6 | ELECTRICAL CHARACTERISTICS                   | 17 |

|-----------|----------------------------------------------|----|

|           | 6.1 Absolute Maximum Rating                  | 17 |

|           | 6.2 Recommended Operating Conditions         |    |

|           | 6.3 DC Characteristics                       | 18 |

|           | 6.4 Analog Circuit Characteristics           | 19 |

|           | 6.5 Power Current Consumption                | 20 |

|           | 6.6 AC Characteristics                       | 21 |

|           | 6.7 Oscillation Characteristics              | 26 |

|           | 6.8 Characteristics Curves (reference value) | 27 |

| CHAPTER 7 | PACKAGE                                      | 28 |

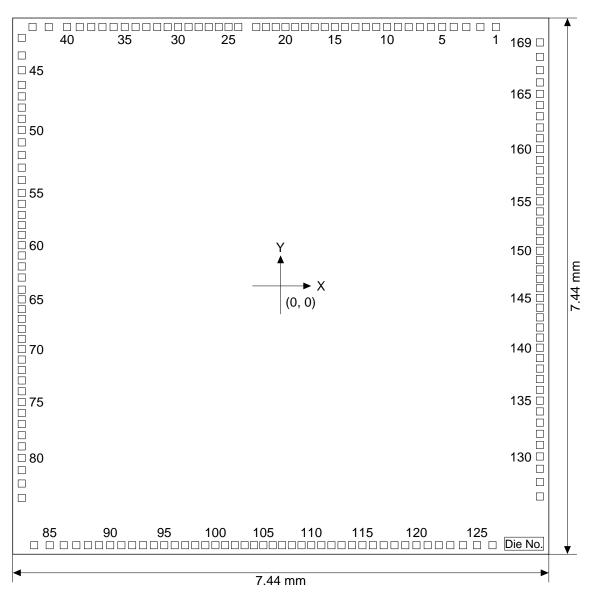

| CHAPTER 8 | PAD LAYOUT                                   | 29 |

|           | 8.1 Diagram of Pad Layout                    | 29 |

|           | 8.2 Pad Coordinates                          |    |

| CHAPTER 9 | Precautions on Mounting                      | 31 |

# CHAPTER 1 OUTLINE

The E0C88P348 is a 8-bit microcomputer, with a built-in Flash EEPROM (PROM), for evaluating the functions of the E0C88348.

The E0C88P348 has almost the same functions as the E0C88348. The mask ROM in the E0C88348 has been changed to a Flash EEPROM that allows the user to rewrite programs using the exclusive PROM writer. The E0C88P348 also supports On Board Programming (the data can be rewritten to the PROM if the IC is mounted on the board). The program can be rewritten up to 10 times under the development stage, it will increase the efficiency of device-level function evaluation.

Note: • Refer to Chapter 4, "Summary of Notes", before rewriting the PROM.

• The E0C88P348 is a program development tool for evaluating the functions, therefore do not use it for mass production.

## 1.1 Features

| OSC1 oscillation circuit               | E0C88 (MODEL3) CMOS 8-bit core CPU 32.768 kHz (Typ.) crystal oscillation circuit * 6 MHz (Max.) crystal/ceramic oscillation circuit * 608 types (usable for multiplication and division instructions) 0.33 μsec/6 MHz (for 2-clock instructions) * 48K bytes Dual power: VDD = 5 V, VPP = 12.5 V for writing/erase |  |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                                        | Serial programming and parallel programming are available *                                                                                                                                                                                                                                                        |  |  |  |  |

| RAM                                    |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Bus line                               | Address bus: 19 bits (shared with output ports)                                                                                                                                                                                                                                                                    |  |  |  |  |

|                                        | Data bus: 8 bits (shared with I/O ports)                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                        | CE signal: 4 bits (shared with output ports)                                                                                                                                                                                                                                                                       |  |  |  |  |

|                                        | WR signal: 1 bit (shared with output port)                                                                                                                                                                                                                                                                         |  |  |  |  |

|                                        | RD signal: 1 bit (shared with output port)                                                                                                                                                                                                                                                                         |  |  |  |  |

| Input port                             |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Output port                            |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 1/0                                    | BACK signal outputs)                                                                                                                                                                                                                                                                                               |  |  |  |  |

| I/O port                               |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Serial interface                       |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| ı imer                                 | Programmable timer (8-bit): 2 ch. (usable as a 1-ch. 16-bit timer)                                                                                                                                                                                                                                                 |  |  |  |  |

|                                        | Clock timer (8-bit): 1 ch.                                                                                                                                                                                                                                                                                         |  |  |  |  |

| I CD driver                            | Stopwatch timer (8-bit): 1 ch.                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                        | 51 segments × 32 commons, 67 segments × 16 or 8 commons                                                                                                                                                                                                                                                            |  |  |  |  |

|                                        | LCD power supply circuit built-in (boostor type, 5 potentials)                                                                                                                                                                                                                                                     |  |  |  |  |

|                                        | Envelope and volume control functions built-in                                                                                                                                                                                                                                                                     |  |  |  |  |

| Watchdog timer                         |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Supply voltage detection (SVD) circuit |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| Internal interrupt                     | Input port interrupt: 2 systems (3 types) Timer interrupt: 3 systems (9 types)                                                                                                                                                                                                                                     |  |  |  |  |

| internal interrupt                     | Serial interface interrupt: 3 systems (3 types)                                                                                                                                                                                                                                                                    |  |  |  |  |

| Power supply voltage                   |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

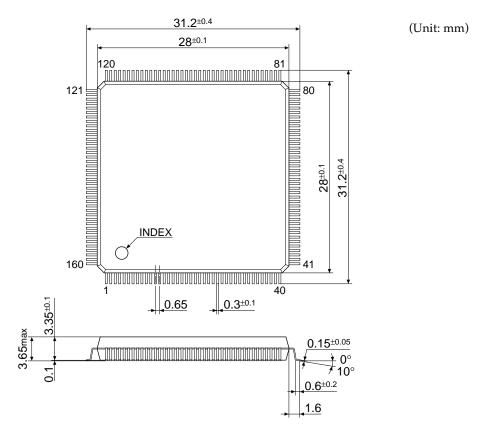

| Package                                |                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| r ackage                               | Q11 0-100pin (plastic) of chip                                                                                                                                                                                                                                                                                     |  |  |  |  |

\*: Items that differ from the E0C88348

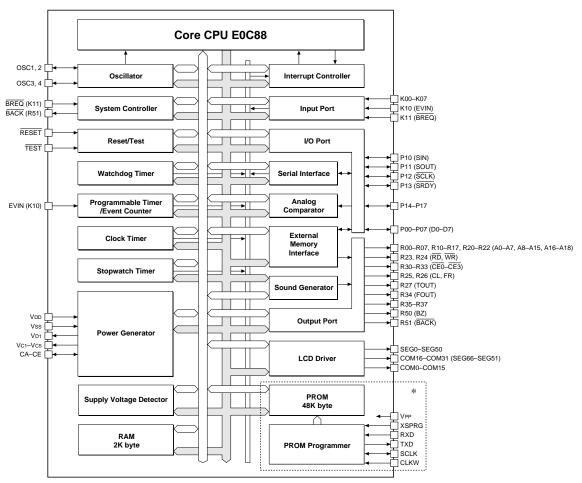

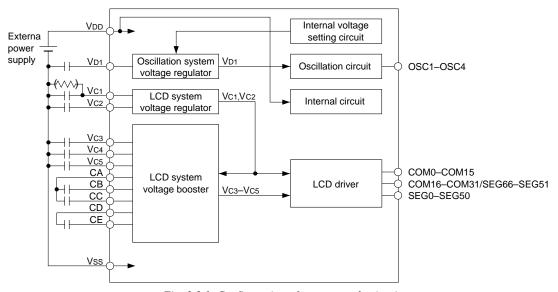

# 1.2 Block Diagram

<sup>\*</sup> The PROM block indicated with a dotted line differ from the E0C88348.

Fig. 1.2.1 Block diagram

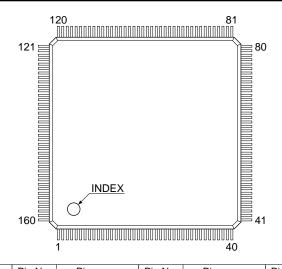

# 1.3 Pin Layout Diagram

# QFP8-160pin

| Pin No. | Pin name    | Pin No. | Pin name          | Pin No. | Pin name          | Pin No.    | Pin name            |

|---------|-------------|---------|-------------------|---------|-------------------|------------|---------------------|

| 1       | SEG18       | 41      | COM24/SEG58       | 81      | OSC1              | 121        | R11/A9              |

| 2       | SEG19       | 42      | COM23/SEG59       | 82      | OSC2              | 122        | R12/A10             |

| 3       | SEG20       | 43      | COM22/SEG60       | 83      | TEST              | 123        | R13/A11             |

| 4       | SEG21       | 44      | COM21/SEG61       | 84      | RESET             | 124        | R14/A12             |

| 5       | SEG22       | 45      | COM20/SEG62       | 85      | V <sub>PP</sub> * | 125        | R15/A13             |

| 6       | SEG23       | 46      | COM19/SEG63       | 86      | K11/BREQ          | 126        | R16/A14             |

| 7       | SEG24       | 47      | COM18/SEG64       | 87      | K10/EVIN          | 127        | R17/A15             |

| 8       | SEG25       | 48      | COM17/SEG65       | 88      | K07               | 128        | R20/A16             |

| 9       | SEG26       | 49      | COM16/SEG66       | 89      | K06               | 129        | R21/A17             |

| 10      | SEG27       | 50      | COM15             | 90      | K05               | 130        | R22/A18             |

| 11      | SEG28       | 51      | COM14             | 91      | K04               | 131        | R23/RD              |

| 12      | SEG29       | 52      | COM13             | 92      | K03               | 132        | $R24/\overline{WR}$ |

| 13      | SEG30       | 53      | COM12             | 93      | K02               | 133        | R25/CL              |

| 14      | SEG31       | 54      | COM11             | 94      | K01               | 134        | R26/FR              |

| 15      | SEG32       | 55      | COM10             | 95      | K00               | 135        | R27/TOUT            |

| 16      | SEG33       | 56      | COM9              | 96      | P17               | 136        | R30/CE0             |

| 17      | SEG34       | 57      | COM8              | 97      | P16               | 137        | R31/CE1             |

| 18      | SEG35       | 58      | COM7              | 98      | P15               | 138        | R32/CE2             |

| 19      | SEG36       | 59      | COM6              | 99      | P14               | 139        | R33/CE3             |

| 20      | SEG37       | 60      | COM5              | 100     | P13/SRDY          | 140        | R34/FOUT            |

| 21      | SEG38       | 61      | COM4              | 101     | P12/SCLK          | 141        | R50/BZ              |

| 22      | SEG39       | 62      | COM3              | 102     | P11/SOUT          | 142        | R51/BACK            |

| 23      | SEG40       | 63      | COM2              | 103     | P10/SIN           | 143        | SEG0                |

| 24      | SEG41       | 64      | COM1              | 104     | P07/D7            | 144        | SEG1                |

| 25      | SEG42       | 65      | COM0              | 105     | P06/D6            | 145        | SEG2                |

| 26      | SEG43       | 66      | CE                | 106     | P05/D5            | 146        | SEG3                |

| 27      | SEG44       | 67      | CD                | 107     | P04/D4            | 147        | SEG4                |

| 28      | SEG45       | 68      | CC                | 108     | P03/D3            | 148        | SEG5                |

| 29      | SEG46       | 69      | CB                | 109     | P02/D2            | 149        | SEG6                |

| 30      | SEG47       | 70      | CA                | 110     | P01/D1            | 150        | SEG7                |

| 31      | SEG48       | 71      | Vc5               | 111     | P00/D0            | 151        | SEG8                |

| 32      | SEG49       | 72      | Vc4               | 112     | R00/A0            | 152        | SEG9                |

| 33      | SEG50       | 73      | Vc3               | 113     | R01/A1            | 153        | SEG10               |

| 34      | COM31/SEG51 | 74      | Vc2               | 114     | R02/A2            | 154        | SEG11               |

| 35      | COM30/SEG52 | 75      | Vc1               | 115     | R03/A3            | 155        | SEG12               |

| 36      | COM29/SEG53 | 76      | OSC3              | 116     | R04/A4            | 156        | SEG13               |

| 37      | COM28/SEG54 | 77      | OSC4              | 117     | R05/A5            | 157        | SEG14               |

| 38      | COM27/SEG55 | 78      | Vd1               | 118     | R06/A6            | 158        | SEG15               |

| 39      | COM26/SEG56 | 79      | $V_{\mathrm{DD}}$ | 119     | R07/A7            | 159        | SEG16               |

| 40      | COM25/SEG57 | 80      | Vss               | 120     | R10/A8            | 160        | SEG17               |

|         |             |         |                   |         | * : Termina       | al changed | in the E0C88P348.   |

\*: Terminal changed in the E0C88P348.

Fig. 1.3.1 Pin layout diagram (QFP8-160pin)

# 1.4 Pin Description

Table 1.4.1 Pin description (QFP8-160pin)

| Pin name                  | Pin No.         | In/out    | .1 Pin description (QFP8-100pin)  Function                                         |

|---------------------------|-----------------|-----------|------------------------------------------------------------------------------------|

| V <sub>DD</sub>           | 79              | - III/OUL | Power supply (+) terminal                                                          |

| Vss                       | 80              | _         | Power supply (+) terminal Power supply (GND) terminal                              |

| V <sub>D1</sub>           | 78              |           | Regulated voltage output terminal for oscillators                                  |

| VC1–VC5                   | 75–71           | 0         | LCD drive voltage output terminals                                                 |

| CA-CE                     | 70–66           | 0         | Booster capacitor connection terminals for LCD                                     |

| OSC1                      | 81              | I         | OSC1 oscillation input terminal                                                    |

| 0301                      | 61              | 1         | (crystal oscillation)                                                              |

| OSC2                      | 82              | О         | OSC1 oscillation output terminal                                                   |

| OSC3                      | 76              | I         | OSC3 oscillation input terminal                                                    |

| 0505                      | , ,             | -         | (crystaloscillation/ceramic oscillation)                                           |

| OSC4                      | 77              | О         | OSC3 oscillation output terminal                                                   |

| K00-K07                   | 95–88           | I         | Input terminals (K00–K07)                                                          |

| K10/EVIN                  | 87              | I         | Input terminal (K10) or event counter external clock input terminal (EVIN)         |

| K11/BREQ                  | 86              | I         | Input terminal (K11) or bus request signal input terminal (BREQ)                   |

| R00–R07/A0–A7             |                 |           |                                                                                    |

| R10–R17/A8–A15            | 112–119         | 0         | Output terminals (R00–R07) or address bus (A0–A7)                                  |

|                           | 120–127         | 0         | Output terminals (R10–R17) or address bus (A8–A15)                                 |

| R20–R22/A16–A18<br>R23/RD | 128–130         |           | Output terminals (R20–R22) or address bus (A16–A18)                                |

|                           | 131             | 0         | Output terminal (R23) or read signal output terminal (RD)                          |

| R24/WR                    | 132             | 0         | Output terminal (R24) or write signal output terminal (WR)                         |

| R25/CL                    | 133             | 0         | Output terminal (R25) or LCD synchronous signal output terminal (CL)               |

| R26/FR                    | 134             | 0         | Output terminal (R26) or LCD frame signal output terminal (FR)                     |

| R27/TOUT                  | 135             | О         | Output terminal (R27)                                                              |

| D.0. D.0./200 200         | 101.100         |           | or programmable timer underflow signal output terminal (TOUT)                      |

| R30-R33/CE0-CE3           | 136–139         | O         | Output terminals (R30–R33) or chip enable output terminals (CE0–CE3)               |

| R34/FOUT                  | 140             | О         | Output terminal (R34) or clock output terminal (FOUT)                              |

| R35–R37 *2                | (only for chip) | О         | Output terminals (R35–R37)                                                         |

| R50/BZ                    | 141             | О         | Output terminal (R50) or buzzer output terminal (BZ)                               |

| R51/BACK                  | 142             | О         | Output terminal (R51) or bus acknowledge signal output terminal (BACK)             |

| P00-P07/D0-D7             | 111–104         | I/O       | I/O terminals (P00–P07) or data bus (D0–D7)                                        |

| P10/SIN                   | 103             | I/O       | I/O terminal (P10) or serial I/F data input terminal (SIN)                         |

| P11/SOUT                  | 102             | I/O       | I/O terminal (P11) or serial I/F data output terminal (SOUT)                       |

| P12/SCLK                  | 101             | I/O       | I/O terminal (P12) or serial I/F clock I/O terminal (SCLK)                         |

| P13/SRDY                  | 100             | I/O       | I/O terminal (P13) or serial I/F ready signal output terminal (SRDY)               |

| P14 *5                    | 99              | I/O       | I/O terminal (P14)                                                                 |

| P15 *5                    | 98              | I/O       | I/O terminal (P15)                                                                 |

| P16 *5                    | 97              | I/O       | I/O terminal (P16)                                                                 |

| P17 *5                    | 96              | I/O       | I/O terminal (P17)                                                                 |

| COM0-COM15                | 65–50           | О         | LCD common output terminals                                                        |

| COM16-COM31               | 49–34           | О         | LCD common output terminals (when 1/32 duty is selected)                           |

| /SEG66–SEG51              |                 |           | or LCD segment output terminal (when 1/16 or 1/8 duty is selected)                 |

| SEG0-SEG50                | 143–160, 1–33   | О         | LCD segment output terminals                                                       |

| RESET                     | 84              | I         | Initial reset input terminal                                                       |

| TEST *1                   | 83              | I         | Test input terminal                                                                |

| VPP *3                    | 85              | _         | PROM programming power supply (fix at +5 V in normal/high-speed mode)              |

| XSPRG *2 *4               | (only for chip) | I         | PROM serial programming mode setting (fix at High in normal/high-speed mode)       |

| RXD *2 *4                 | (only for chip) | I         | PROM serial programming data input (fix at High in normal/high-speed mode)         |

| TXD *2 *4                 | (only for chip) | О         | PROM serial programming data output (unused in normal/high-speed mode)             |

| SCLK *2 *4                | (only for chip) | I/O       | PROM serial programming clock I/O (fix at High in normal/high-speed mode)          |

| CLKW *2 *4                | (only for chip) | I         | PROM serial programming source clock input (fix at High in normal/high-speed mode) |

<sup>\*1:</sup> TEST is the terminal used for shipping inspection of the IC. For normal operation be sure it is connected to VDD.

See Section 3.1, "Terminal Configuration", for the terminal functions during the programming mode.

<sup>\*2:</sup> These terminals can be used only when the E0C88P348 is shipped with a chip form.

<sup>\*3:</sup> This terminal is changed in the E0C88P348.

<sup>\*4:</sup> These terminals are added in the E0C88P348.

<sup>\*5:</sup> Functions are limited in the E0C88P348.

# CHAPTER 2 PROM PROGRAMMER AND OPERATING MODES

The biggest difference between the E0C88348 and the E0C88P348 is that the E0C88P348 contains Flash EEPROM as the ROM that allows the user to write data to it using the exclusive ROM writer (UNIVERSAL ROM WRITER II). The E0C88P348 also has a built-in PROM programmer that controls writing data to the PROM.

This chapter explains the PROM programmer and the operating modes that are added for the programming operation.

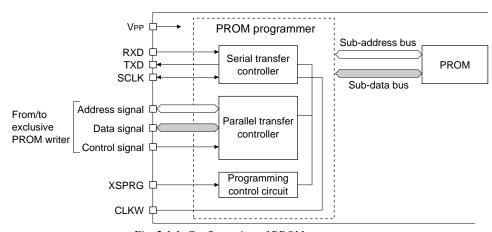

# 2.1 Configuration of PROM Programmer

Figure 2.1.1 shows the configuration of the PROM programmer.

Fig. 2.1.1 Configuration of PROM programmer

The PROM programmer supports Serial Programming for writing data received in serial transfer and Parallel Programming that uses a parallel transfer. The programming method will be described later.

#### **Terminals**

The PROM programmer uses the following input/output terminals. The following sections will explain handling the terminals in each operating mode.

VPP: Power supply terminal for PROM programming

XSPRG: PROM serial programming mode setting terminal

RXD: Serial data receive terminal TXD: Serial data transmit terminal

SCLK: Serial clock input/output terminal

CLKW: Serial programming source clock (3.072 MHz) input terminal

The parallel programming mode uses other terminals in addition to the terminals above. However, it is not necessary to switch the lines on the board, because the IC is programed by directly installing it to the exclusive PROM writer (UNIVERSAL ROM WRITER II).

# 2.2 Operating Modes

Three operating modes are available in the E0C88P348: one is for normal operation and the others are for programming.

- 1) Normal operation mode (Normal mode/High-speed mode)

- 2) PROM serial programming mode

- 3) PROM parallel programming mode

The operating mode is decided by the XSPRG terminal setting at power on or initial reset.

# 2.2.1 Normal operation mode

In this mode, the E0C88 core CPU and the peripheral circuits operate by the programmed PROM. The CPU can enter this mode after the PROM programming has finished.

The PROM bit data is set to "1" at shipment. Therefore, the IC will not work even if the normal operation mode is set before programming.

In the normal operation mode, set the terminals for the PROM programmer as below. The board must be designed so that the terminal settings cannot be changed.

VPP: Supply a voltage the same as VDD. In order to prevent damage to the IC, do not

supply 12.5 V of programming voltage in the normal operation mode.

XSPRG: Fix at a High level.

RXD, SCLK, CLKW: Open or fix at a High level.

TXD: Open.

# 2.2.2 PROM serial programming mode

The PROM serial programming mode should be set when writing data to the PROM using a serial transfer from the exclusive PROM writer (UNIVERSAL ROM WRITER II). This mode will be used for the programming of chip products, because the programming can be done even when the IC has already been mounted on the board.

To create data to be written to the PROM, use the E0C88 assembler similar to the E0C88348.

The following explains the procedure of PROM serial programming.

### PROM serial programming procedure

(1) Set the required terminals for serial programming as follows:

VPP: Connect to VPP on the PROM writer. The voltage (5 V/12.5 V) can be switched using the PROM writer.

Note: Be sure to set VPP to 5 V at the IC power on or initial reset. Note that the IC may be damaged if 12.5 V has been supplied to the VPP terminal at power on or initial reset.

XSPRG: Set the terminal so that it will be fixed to a Low level. (A switch should be provided on the target board to change the XSPRG terminal level between High and Low.)

Note: The XSPRG terminal must be fixed at a Low level in the programming mode and at a High level in the normal operation mode. Changing the voltage level may damage the IC.

RXD, TXD, SCLK: Connect to the PROM writer.

**CLKW**: Connect to the PROM writer. A 3.072 MHz clock will be supplied from the PROM writer at programming.

Other terminals should be set as below.

Input port terminals (K): Fix at a High or Low level. I/O port terminals (P): Fix at a High or Low level.

TEST terminal: Fix at a High level.

- (2) Turn the IC (user target board) power (+5 V) on.

A power voltage must be supplied to the VDD and Vss terminals same as the regular operation so that the OSC1 oscillation circuits operate normally.

- (3) Turn the PROM writer on.

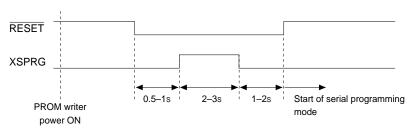

- (4) Controls the  $\overline{RESET}$  and XSPRG terminals as shown in Figure 2.2.2.1.

Fig. 2.2.2.1 Timing chart for entering serial programming mode

(5) Start up the romw88.exe in the personal computer, then load the 88p348.frm file. This allows serial programming to begin.

After setting this mode, data can be written to the exclusive PROM writer (UNIVERSAL ROM WRITER II). Refer to the "E0C88Pxxx Universal ROM Writer II User's Manual" for the connection and operation of the PROM writer.

# 2.2.3 PROM parallel programming mode

In the PROM parallel programming mode, the exclusive PROM writer (UNIVERSAL ROM WRITER II) transfers data in parallel to the IC installed on the PROM writer to write data to it. The terminal setting is done by the PROM writer. Thus there is no precaution on mode setting or board design. Refer to the "E0C88Pxxx Universal ROM Writer II User's Manual" for the operation of the PROM writer. To create data to be written to the PROM, use the E0C88 assembler the same as the E0C88348.

Note: The QFP8-160pin package supports the parallel programing mode only.

# CHAPTER 3 DIFFERENCES FROM E0C88348

This chapter explains the differences on functions between the E0C88P348 and the E0C88348. The functions without description are the same in both models. Refer to the "E0C88348 Technical Manual" for the circuits and functions.

# 3.1 Terminal Configuration

The E0C88P348 has terminals for the PROM programmer in addition to the ones on the E0C88348. The other terminals are the same configuration as the E0C88348 (except for the VPP terminal). Table 3.1.1 shows the pad configuration and the terminal functions according to the operating mode.

Table 3.1.1 Terminal configuration

|                                         |            |                  | Normal operation mode |                                       | Serial programming mode |                                            |  |  |

|-----------------------------------------|------------|------------------|-----------------------|---------------------------------------|-------------------------|--------------------------------------------|--|--|

| Pin name                                |            | Pad No.          | I/O                   | · · · · · · · · · · · · · · · · · · · |                         | I/O Function                               |  |  |

| V <sub>DD</sub>                         |            | 42               | _                     | Power (+5V)                           | _                       | Power (+5V)                                |  |  |

| Vss                                     |            | 43               | _                     | Power (GND)                           | _                       | Power (GND)                                |  |  |

| V <sub>D1</sub>                         |            | 41               | _                     | Regulated voltage output              | _                       | Regulated voltage output                   |  |  |

| VC1-VC5                                 |            | 38-34            | 0                     | LCD drive voltage                     | О                       | Unused                                     |  |  |

| CA-CE                                   |            | 33–29            | _                     | Capacitor for LCD voltage             | _                       | Unused                                     |  |  |

| OSC1                                    |            | 44               | I                     | OSC1 oscillation input                | I                       | OSC1 oscillation input                     |  |  |

| OSC2                                    |            | 45               | 0                     | OSC1 oscillation output               | О                       | OSC1 oscillation output                    |  |  |

| OSC3                                    |            | 39               | I                     | OSC3 oscillation input                | I                       | Unused                                     |  |  |

| OSC4                                    |            | 40               | О                     | OSC3 oscillation output               | О                       | Unused                                     |  |  |

| K00-K07                                 |            | 58-51            | I                     | Input port                            | I                       | Unused (High or Low)                       |  |  |

| K10/EVIN                                |            | 50               | I                     | Input port or EVIN input              | I                       | Unused (High or Low)                       |  |  |

| K11/BREQ                                |            | 49               | I                     | Input port or BREQ input              | I                       | Unused (High or Low)                       |  |  |

| R00-R07/A0-A7                           |            | 75–82            | О                     | Output port or address bus            | 0                       | Unused                                     |  |  |

| R10-R17/A8-A15                          |            | 83-90            | О                     | Output port or address bus            | О                       | Unused                                     |  |  |

| R20-R22/A16-A1                          | 8          | 91–93            | О                     | Output port or address bus            | О                       | Unused                                     |  |  |

| R23/RD                                  |            | 94               | О                     | Output port or RD output              | О                       | Unused                                     |  |  |

| R24/WR                                  |            | 95               | О                     | Output port or WR output              | О                       | Unused                                     |  |  |

| R25/CL                                  |            | 96               | О                     | Output port or CL output              | О                       | Unused                                     |  |  |

| R26/FR                                  |            | 97               | О                     | Output port or FR output              | О                       | Unused                                     |  |  |

| R27/TOUT                                |            | 98               | О                     | Output port or TOUT output            | О                       | Unused                                     |  |  |

| R30-R33/ <del>CE0</del> - <del>CE</del> | <u>-</u> 3 | 99-102           | О                     | Output port or CE output              | О                       | Unused                                     |  |  |

| R34/FOUT                                |            | 103              | О                     | Output port or FOUT output            | О                       | Unused                                     |  |  |

| R35-R37                                 |            | 104–106          | О                     | Output port                           | О                       | Unused                                     |  |  |

| R50/BZ                                  |            | 107              | 0                     | Output port or BZ output              | О                       | Unused                                     |  |  |

| R51/BACK                                |            | 108              | О                     | Output port or BACK output            | О                       | Unused                                     |  |  |

| P00-P07/D0-D7                           |            | 74–67            | I/O                   | I/O port or data bus                  | I                       | Unused (High or Low)                       |  |  |

| P10/SIN                                 |            | 66               | I/O                   | I/O port or SIN input                 | I                       | Unused (High or Low)                       |  |  |

| P11/SOUT                                |            | 65               | I/O                   | I/O port or SOUT output               | I                       | Unused (High or Low)                       |  |  |

| P12/SCLK                                |            | 64               | I/O                   | I/O port or SCLK terminal             | I                       | Unused (High or Low)                       |  |  |

| P13/SRDY                                |            | 63               | I/O                   | I/O port or SRDY output               | I                       | Unused (High or Low)                       |  |  |

| P14 *                                   | ×1         | 62               | I/O                   | I/O port                              | I                       | Unused (High or Low)                       |  |  |

| P15 *                                   | ×1         | 61               | I/O                   | I/O port                              | I                       | Unused (High or Low)                       |  |  |

| P16 *                                   | ×1         | 60               | I/O                   | I/O port                              | I                       | Unused (High or Low)                       |  |  |

| P17 :                                   | k1         | 59               | I/O                   | I/O port                              | I                       | Unused (High or Low)                       |  |  |

| COM0-COM15                              |            | 28-24, 20-10     | О                     | LCD COM output                        | О                       | Unused                                     |  |  |

| COM16-COM31                             |            | 9-1, 169-163     | О                     | LCD COM output                        | О                       | Unused                                     |  |  |

| /SEG66-SEG51                            |            |                  |                       | or LCD SEG output                     |                         |                                            |  |  |

| SEG0-SEG50                              |            | 109-146, 150-162 | О                     | LCD SEG output                        | О                       | Unused                                     |  |  |

| RESET                                   |            | 47               | I                     | Initial reset                         | I                       | Initial reset                              |  |  |

| TEST                                    |            | 46               | I                     | Test port (High)                      | I                       | Unused (High)                              |  |  |

| VPP :                                   | k2         | 48               | _                     | PROM power (+5 V)                     | -                       | PROM program power (+5/12.5 V)             |  |  |

| XSPRG *                                 | ×2         | 147              | I                     | Unused (High)                         | I                       | PROM serial programming mode setting       |  |  |

| RXD *                                   | k2         | 21               | I                     | Unused (High)                         | I                       | PROM serial programming data input         |  |  |

|                                         | k2         | 23               | О                     | Unused                                | О                       | PROM serial programming data output        |  |  |

| SCLK *                                  | k2         | 22               | I                     | Unused (High)                         | I/O                     | PROM serial programming clock I/O          |  |  |

|                                         | k2         | 148              | I                     | Unused (High)                         | I                       | PROM serial programming source clock input |  |  |

<sup>\*1:</sup> The functions of these terminals are limited in the E0C88P348. \*2: These terminals differ from the E0C88348.

In the parallel programming mode, all the terminals are set to the appropriate status by the exclusive PROM writer.

# 3.2 Mask Option

The E0C88P348 cannot specify the E0C88348 mask options individually. The following option combination is provided for the E0C88P348:

Table 3.2.1 Combination of mask options

| Mask option                                                               |       | Setting                          |

|---------------------------------------------------------------------------|-------|----------------------------------|

| OSC1 oscillation circuit                                                  |       | Crystal oscillation (32.768 kHz) |

| OSC3 oscillation circuit  Multiple key entry reset combination  SVD reset |       | Crystal/ceramic oscillation      |

|                                                                           |       | Not use                          |

|                                                                           |       | Not use                          |

| Input port pull up resistor                                               | K00   | With resistor                    |

|                                                                           | K01   | With resistor                    |

|                                                                           | K02   | With resistor                    |

|                                                                           | K03   | With resistor                    |

|                                                                           | K04   | With resistor                    |

|                                                                           | K05   | With resistor                    |

|                                                                           | K06   | With resistor                    |

|                                                                           | K07   | With resistor                    |

|                                                                           | K10   | With resistor                    |

|                                                                           | K11   | With resistor                    |

|                                                                           | RESET | With resistor                    |

| I/O port pull up resistor                                                 | P00   | With resistor                    |

| O port pull up resistor                                                   | P01   | With resistor                    |

|                                                                           | P02   | With resistor                    |

|                                                                           | P03   | With resistor                    |

|                                                                           | P04   | With resistor                    |

|                                                                           | P05   | With resistor                    |

|                                                                           | P06   | With resistor                    |

|                                                                           | P07   | With resistor                    |

|                                                                           | P10   | With resistor                    |

|                                                                           | P11   | With resistor                    |

|                                                                           | P12   | With resistor                    |

|                                                                           | P13   | With resistor                    |

|                                                                           | P14   | With resistor                    |

|                                                                           | P15   | With resistor                    |

|                                                                           | P16   | With resistor                    |

| Dutnut port specification                                                 | P17   | With resistor                    |

| Output port specification                                                 | R00   | Complementary                    |

|                                                                           | R01   | Complementary                    |

|                                                                           | R02   | Complementary                    |

|                                                                           | R03   | Complementary                    |

|                                                                           | R04   | Complementary                    |

|                                                                           | R05   | Complementary                    |

|                                                                           | R06   | Complementary                    |

|                                                                           | R07   | Complementary                    |

|                                                                           | R10   | Complementary                    |

|                                                                           | R11   | Complementary                    |

|                                                                           | R12   | Complementary                    |

|                                                                           | R13   | Complementary                    |

|                                                                           | R14   | Complementary                    |

|                                                                           | R15   | Complementary                    |

|                                                                           | R16   | Complementary                    |

|                                                                           | R17   | Complementary                    |

| LCD drive duty                                                            |       | 1/32 & 1/16 duty                 |

| LCD power supply                                                          |       | Internal TYPE B (5.5 V)          |

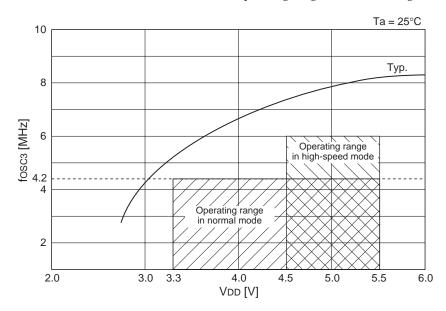

# 3.3 Power Supply

### Supply voltage (VDD)

The operable voltage range is different.

E0C88348: Normal mode 2.4 V to 5.5 V

Low-power mode 1.8 V to 3.5 V

High-speed mode 3.5 V to 5.5 V E0C88P348: Normal mode 3.3 V to 5.5 V

High-speed mode 4.5 V to 5.5 V

The E0C88P348 operation is guaranteed within the above voltage range. The operating mode should be set in the normal mode or the high-speed mode.

### Supply voltage for PROM (VPP)

The power supply terminal for PROM is added in the E0C88P348.

VPP: PROM programming voltage in normal operation mode: VDD

in programming mode: 12.5 V

### Power supply for oscillation circuit (VD1)

The VD1 voltage value can only be set to 2.2 V (normal mode) or 3.3 V (high-speed mode) in the E0C88P348 because the operating voltage range is limited.

Note: In the E0C88348, the internal circuits operate with the oscillation system regulated voltage (VD1). On the other hand, the E0C88P348 internal circuits operate with the supply voltage (VDD). Therefore, the operating frequency range of the E0C88P348 differs from that of the E0C88348. Refer to Chapter 6, "Electrical Characteristics", for details.

Fig. 3.3.1 Configuration of power supply circuit

# LCD drive voltage (Vc1-Vc5)

The range of the LCD drive voltage is different from that of the E0C88348.

Table 3.3.1 Range of LCD drive voltage

| LCD                      |                      |                                              |             | 8348        | E0C88P348   |             |  |

|--------------------------|----------------------|----------------------------------------------|-------------|-------------|-------------|-------------|--|

| drive voltage            | Condition            |                                              | Min.        | Max.        | Min.        | Max.        |  |

| Vc1                      | *1                   |                                              | 0.18Vc5     | 0.22Vc5     | 0.18Vc5     | 0.22Vc5     |  |

| Vc2                      | *2                   |                                              | 0.39Vc5     | 0.48Vc5     | 0.38Vc5     | 0.46Vc5     |  |

| Vc3                      | *3                   |                                              | 0.59Vc5     | 0.63Vc5     | 0.58Vc5     | 0.63Vc5     |  |

| VC4                      | *4                   |                                              | 0.80Vc5     | 0.84Vc5     | 0.77Vc5     | 0.89Vc5     |  |

| VC5<br>TYPE A<br>(4.5 V) | *5                   | LCX = 0H $LCX = 1H$ $LCX = 2H$               |             |             |             |             |  |

|                          |                      | LCX = 3H<br>LCX = 4H<br>LCX = 5H             |             |             |             |             |  |

|                          |                      | LCX = 6H<br>LCX = 7H                         | Typ. × 0.94 | Typ. × 1.06 | Not set     | Not set     |  |

|                          |                      | LCX = 8H<br>LCX = 9H<br>LCX = AH             |             |             |             |             |  |

|                          |                      | LCX = BH<br>LCX = CH<br>LCX = DH<br>LCX = EH |             |             |             |             |  |

| X7                       | . ~                  | LCX = FH                                     |             |             |             |             |  |

| VC5<br>TYPE B            | *5                   | LCX = 0H<br>LCX = 1H                         |             |             |             |             |  |

| (5.5 V)                  |                      | LCX = 2H<br>LCX = 3H                         |             |             |             |             |  |

|                          |                      | LCX = 4H<br>LCX = 5H                         |             |             |             |             |  |

|                          |                      | LCX = 6H<br>LCX = 7H                         | Typ. × 0.94 | Typ. × 1.06 | Typ. × 0.90 | Typ. × 1.10 |  |

|                          |                      | LCX = 8H<br>LCX = 9H                         |             |             |             |             |  |

|                          | LCX = AH<br>LCX = BH | LCX = BH                                     |             |             |             |             |  |

|                          |                      | LCX = CH                                     |             |             |             |             |  |

|                          |                      | LCX = DH                                     |             |             |             |             |  |

|                          |                      | LCX = EH                                     |             |             |             |             |  |

|                          |                      | LCX = FH                                     |             |             |             |             |  |

<sup>\*1:</sup> when a 1  $\mbox{M}\Omega$  load resistor is connected between Vss and Vc1

For details on the LCD drive voltage, refer to Section 6.4, "Analog Circuit Characteristics", in this manual and Section 7.4 in the "E0C88348 Technical Manual".

<sup>(</sup>Unit: V)

<sup>\*2:</sup> when a 1  $M\Omega$  load resistor is connected between Vss and Vc2

<sup>\*3:</sup> when a 1  $\text{M}\Omega$  load resistor is connected between Vss and Vc3

<sup>\*4:</sup> when a 1  $M\Omega$  load resistor is connected between Vss and Vc4

<sup>\*5:</sup> when a 1  $M\Omega$  load resistor is connected between Vss and Vc5

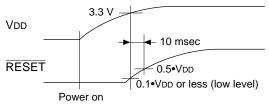

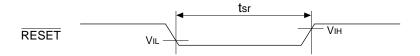

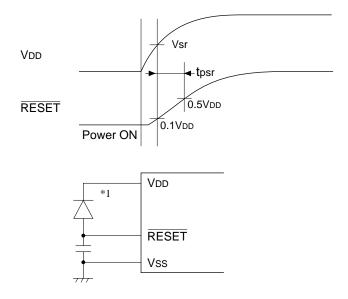

# 3.4 Initial Reset

When turning the E0C88P348 power on, the  $\overline{RESET}$  terminal must be maintained at a Low level until the supply voltage goes to 3.3 V or more.

Fig. 3.4.1 Initial reset at power-on

The E0C88P348 uses initial reset as a trigger for setting either the normal operation mode or the programming mode. Therefore, design the reset input circuit so that the IC will be reset for sure. Initial resetting during operation is the same as the E0C88348.

When resetting the IC in the normal operation mode, make sure to fix the XSPRG terminal at a High level. Moreover, the VPP terminal for PROM programming power supply must be fixed at 5 V during initial reset even when setting the programming mode. Do not reset the IC when 12.5 V is being supplied to the VPP terminal.

## 3.5 ROM

The E0C88P348 has employed a PROM for the internal ROM. The memory capacity is the same as the E0C88348 at 48K bytes.

The PROM can be rewritten up to 10 times. Rewriting data is done at the user's own risk.

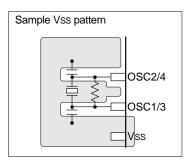

# 3.6 Oscillation Circuit

In the E0C88P348, a crystal oscillator can only be used for the OSC1 oscillation circuit and a crystal or ceramic oscillator for the OSC3 oscillation circuit.

Furthermore, pay attention to the difference on the oscillation start time according to the supply voltage. Be sure there is enough margin especially for stabilizing the OSC3 oscillation when controlling the peripheral circuit that uses the OSC3 clock.

# 3.7 SVD Circuit

The E0C88P348 has a built-in SVD circuit similar to the E0C88348, but each detection level is different from the E0C88348. Furthermore, the range of detection levels is limited because the operating voltage range is different.

Table 3.7.1 SVD detection level of E0C88348/88P348

| Detection level                       |             | E0C88348  |             | E0C88P348          |         |                    |  |

|---------------------------------------|-------------|-----------|-------------|--------------------|---------|--------------------|--|

| Detection level                       | Min.        | Min. Typ. |             | Min.               | Тур.    | Max.               |  |

| Level $1 \rightarrow \text{Level } 0$ |             | 1.82      |             |                    | Not set |                    |  |

| Level 2 $\rightarrow$ Level 1         |             | 2.00      |             |                    | Not set |                    |  |

| Level 3 $\rightarrow$ Level 2         |             | 2.18      |             |                    | Not set |                    |  |

| Level 4 → Level 3                     |             | 2.36      |             |                    | Not set |                    |  |

| Level 5 $\rightarrow$ Level 4         | Typ. × 0.92 | 2.54      | Typ. × 1.08 |                    | Not set |                    |  |

| Level 6 → Level 5                     |             | 2.72      |             |                    | Not set |                    |  |

| Level 7 → Level 6                     |             | 2.90      |             | Not set            |         |                    |  |

| Level 8 → Level 7                     |             | 3.08      |             |                    | Not set |                    |  |

| Level 9 → Level 8                     |             | 3.26      |             |                    | 3.26    |                    |  |

| Level $10 \rightarrow$ Level 9        |             | 3.45      |             |                    | 3.45    |                    |  |

| Level 11 → Level 10                   |             | 3.65      |             |                    | 3.65    |                    |  |

| Level $12 \rightarrow$ Level 11       | Typ. × 0.88 | 3.85      | Typ. × 1.12 | Typ. $\times$ 0.80 | 3.85    | Typ. $\times$ 1.20 |  |

| Level $13 \rightarrow$ Level $12$     |             | 4.05      |             |                    | 4.05    |                    |  |

| Level 14 → Level 13                   |             | 4.25      |             |                    | 4.25    |                    |  |

| Level 15 → Level 14                   |             | 4.50      |             |                    | 4.50    |                    |  |

(Unit: V)

The mask option for reseting when low voltage is detected (available in the E0C88348) is not provided in the E0C88P348. Therefore, the function cannot be used with the E0C88P348.

# CHAPTER 4 SUMMARY OF NOTES

# 4.1 Notes Related to the PROM

- (1) The PROM bit data is set to "1" at shipment. Therefore, It must be programmed before operating the IC in the normal operation mode.

- (2) The PROM data can be rewritten up to 10 times.

- (3) The circuit board should be designed so that the terminals can switch the input signals that differ between the PROM serial programming mode and the normal operation mode.

- (4) The terminals for the PROM programmer should be set correctly according to the operating mode and fixed so that they cannot be changed during operation. Especially the XSPRG terminal must be fixed at a Low level in the programming mode, while they must be fixed at a High level in the normal operation mode. Changing the voltage level may damage the IC.

- (5) Be sure to set VPP to 5 V at the IC power on or initial reset regardless of the operating mode to be set. Note that the IC may be damaged if 12.5 V has been supplied to the VPP terminal at power on or initial reset. To prevent damage of the IC, do not supply 12.5 V of programming voltage in the normal operation mode.

- (6) If the operation of the E0C88P348 is unstable even though the writing and verification of the PROM data was completed normally, write and verify the PROM data without erasing the PROM.

- (7) Rewriting the PROM is done at on the user's own risk.

# 4.2 Notes on Differences form the E0C88348

Be aware of the following notes when using the E0C88P348 as a development tool for the E0C88348.

### **Power supply**

The E0C88P348 is operable with a supply voltage within the range of 3.3 V to 5.5 V. Be aware that as the supply voltage is different from the E0C88348 the electrical characteristics differ.

#### Initial reset

Note that the power-on reset time differs from the E0C88348 because the supply voltage is different. For the electrical characteristics, refer to "Power-on reset" in Section 6.6.

Furthermore, the reset functions using the input port (K00–K03) simultaneous low input or SVD circuit cannot be used because the mask option is fixed at "Not used".

#### Oscillation circuit

In the E0C88P348, a crystal oscillator can only be used for the OSC1 oscillation circuit and a crystal or ceramic oscillator for the OSC3 oscillation circuit.

Furthermore, pay attention to the difference on the oscillation start time according to the supply voltage. Be sure there is enough margin especially for stabilizing the OSC3 oscillation when controlling the peripheral circuit that uses the OSC3 clock.

### LCD controller

The LCD drive voltage range of the E0C88P348 is different from that of the E0C88348. Check the electrical characteristic differences by referring to this manual and the "E0C88348 Technical Manual" before designing the LCD unit. Moreover, note that because mask options are not available, the LCD drive duty and LCD power specification of the E0C88P348 are fixed at 1/32 or 1/16 duty and the internal power supply is TYPE B (5.5 V).

### **SVD** circuit

The SVD detection levels of the E0C88P348 are different from those of the E0C88348 because the operating voltage is different. When using the SVD function, check the available detection level.

### Mask option

In the E0C88P348, the specifications selected by the E0C88348 mask options are fixed and cannot be selected. Therefore, some optional functions cannot be used in the E0C88P348. Check whether the functions are enabled or not in this manual and the "E0C88348 Technical Manual".

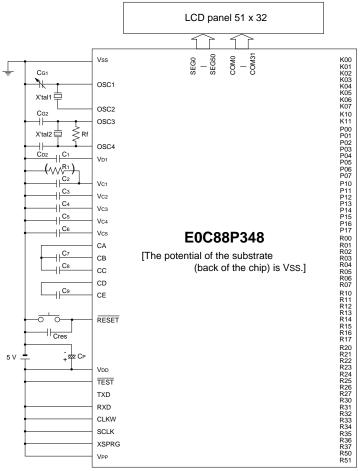

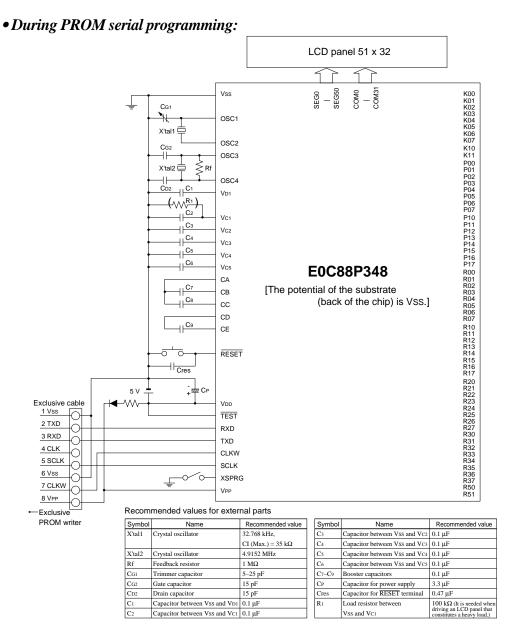

# CHAPTER 5 BASIC EXTERNAL WIRING DIAGRAM

# • During normal operation:

Recommended values for external parts

| Symbol | Name                          | Recommended value | Symbol | Name                          | Recommended value                                       |

|--------|-------------------------------|-------------------|--------|-------------------------------|---------------------------------------------------------|

| X'tal1 | Crystal oscillator            | 32.768 kHz,       | C3     | Capacitor between Vss and Vc2 | 0.1 μF                                                  |

|        |                               | CI (Max.) = 35 kΩ | C4     | Capacitor between Vss and Vc3 | 0.1 μF                                                  |

| X'tal2 | Crystal oscillator            | 4.9152 MHz        | C5     | Capacitor between Vss and Vc4 | 0.1 μF                                                  |

| Rf     | Feedback resistor             | 1 ΜΩ              | C6     | Capacitor between Vss and Vcs | 0.1 μF                                                  |

| CG1    | Trimmer capacitor             | 5-25 pF           | C7-C9  | Booster capacitors            | 0.1 μF                                                  |

| CG2    | Gate capacitor                | 15 pF             | CP     | Capacitor for power supply    | 3.3 μF                                                  |

| CD2    | Drain capacitor               | 15 pF             | Cres   | Capacitor for RESET terminal  | 0.47 μF                                                 |

| Cı     | Capacitor between Vss and VDI | 0.1 μF            | Rı     | Load resistor between         | $100 \text{ k}\Omega$ (It is needed when                |

| C2     | Capacitor between Vss and Vci | 0.1 μF            |        | Vss and Vci                   | driving an LCD panel that<br>constitutes a heavy load.) |

Note: The above table is simply an example.

Note: The above table is simply an example.

# CHAPTER 6 ELECTRICAL CHARACTERISTICS

Note: The electrical characteristics of the E0C88P348 are different from those of the E0C88348. The following characteristics should be used as reference values when using the E0C88P348 as a development tool. ("\*" indicates that the characteristic value is different from the E0C88348.)

# 6.1 Absolute Maximum Rating

|                              |        |                        |                   | (Vss = | = 0  V |

|------------------------------|--------|------------------------|-------------------|--------|--------|

| Item                         | Symbol | Condition              | Rated value       | Unit   | Note   |

| Power voltage                | VDD    |                        | -0.3 to +6.4*     | V      |        |

| Liquid crystal power voltage | Vc5    |                        | -0.3 to +6.4*     | V      |        |

| Input voltage                | VI     |                        | -0.3 to VDD + 0.3 | V      |        |

| Output voltage               | Vo     |                        | -0.3 to VDD + 0.3 | V      |        |

| High level output current    | Іон    | 1 terminal             | -5                | mA     |        |

|                              |        | Total of all terminals | -20               | mA     |        |

| Low level output current     | Iol    | 1 terminal             | 5                 | mA     |        |

|                              |        | Total of all terminals | 20                | mA     |        |

| Permitted loss               | PD     |                        | 200               | mW     | 1      |

| Operating temperature        | Topr   |                        | 20 to 30*         | °C     |        |

| Storage temperature          | Tstg   |                        | -65 to +150       | °C     | 2      |

Note) 1 In case of plastic package.

# 6.2 Recommended Operating Conditions

|                               |            |                                          |        | (Vss =            | 0 V, Ta = | 20 to 30 | )°C *) |

|-------------------------------|------------|------------------------------------------|--------|-------------------|-----------|----------|--------|

| Item                          | Symbol     | Condition                                | Min.   | Тур.              | Max.      | Unit     | Note   |

| Operating power voltage       | Vdd        |                                          | 3.3*   |                   | 5.5       | V        |        |

| (Normal mode)                 |            |                                          |        |                   |           |          |        |

| Operating power voltage       | Vdd        |                                          | 4.5*   |                   | 5.5       | V        |        |

| (High-speed mode)             |            |                                          |        |                   |           |          |        |

| PROM power voltage*           | VPP        | Normal operation mode                    |        | V <sub>DD</sub> * |           | V        |        |

|                               |            | Programming mode                         | 12.2*  | 12.5*             | 12.8*     | V        |        |

| Operating frequency           | fosci      | $V_{DD} = 3.3 \text{ to } 5.5 \text{ V}$ | 30.000 | 32.768            | 50.000    | kHz      |        |

| (Normal mode)                 | fosc3      |                                          | 0.03   |                   | 4.2*      | MHz      |        |

| Operating frequency           | fosci      | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}$ | 30.000 | 32.768            | 50.000    | kHz      |        |

| (High-speed mode)             | fosc3      |                                          | 0.03   |                   | 6.0*      | MHz      |        |

| Capacitor between VD1 and Vss | Cı         |                                          |        | 0.1               |           | μF       |        |

| Capacitor between VC1 and Vss | C2         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between Vc2 and Vss | C3         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between Vc3 and Vss | C4         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between VC4 and Vss | C5         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between Vc5 and Vss | C6         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between CA and CB   | <b>C</b> 7 |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between CA and CC   | C8         |                                          |        | 0.1               |           | μF       | 3      |

| Capacitor between CD and CE   | C9         |                                          |        | 0.1               |           | μF       | 3      |

| Resistor between VC1 and Vss  | Rı         |                                          |        | 100               |           | kΩ       | 4      |

Note) 3 No capacitor is required when the LCD power supply is not used. In this case, do not connect anything to the Vc1–Vc5 and CA–CE terminals.

<sup>2</sup> This rated value cannot insure the PROM data holding function.

<sup>4</sup> It is necessary when the panel load is large and for 1/32 duty driving.

The resistance value should be decided by connecting it to the actual panel to be used.

# 6.3 DC Characteristics

*Unless otherwise specified:* VDD = 3.3\* to 5.5 V, Vss = 0 V, Ta = 25°C

| Item                             | Symbol          | Condition                             | Min.    | Тур. | Max.   | Unit | Note |

|----------------------------------|-----------------|---------------------------------------|---------|------|--------|------|------|

| High level input voltage         | Vih             | Kxx, Pxx, XSPRG, RXD, SCLK,           | 0.8Vdd  |      | Vdd    | V    |      |

|                                  |                 | CLKW                                  |         |      |        |      |      |

| Low level input voltage          | VIL             | Kxx, Pxx, XSPRG, RXD, SCLK,           | 0       |      | 0.2Vdd | V    |      |

|                                  |                 | CLKW                                  |         |      |        |      |      |

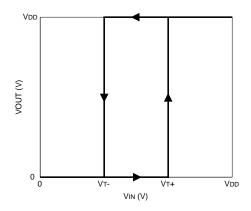

| High level schmitt input voltage | V <sub>T+</sub> | RESET                                 | 0.4Vdd* |      | 0.9Vdd | V    |      |

| Low level schmitt input voltage  | VT-             | RESET                                 | 0.1Vdd  |      | 0.5Vdd | V    |      |

| High level output current        | Іон             | Pxx, Rxx, TXD, Voh = 0.9 Vdd          |         |      | -0.5   | mA   |      |

| Low level output current         | IOL             | Pxx, Rxx, TXD, Vol = 0.1 Vdd          | 0.5     |      |        | mA   |      |