# SRM2AW216LLBT1/7

## 2M-bit Static RAM

- Super Low Voltage Operation and Low Current Consumption

- ●Access Time 100ns (1.8V) / 70ns (2.2V)

- ●131,072 Words x 16-bit Asynchronous

- Wide Temperature Range

#### **■ DESCRIPTION**

The SRM2AW216LBT1/7 is a 131,072 words x 16-bit asynchronous, random access memory on a monolithic CMOS chip. Its very low standby power requirement makes it ideal for applications requiring non-volatile storage with back-up batteries. The asynchronous and static nature of the memory requires no external clock and no refreshing circuit. It is possible to contorol the data width by the data byte control. 3-state output allows easy expansion of memory capacity. The temperature range of the SRM2AW216LLBT1/7 is from –40 to 85°C, and it is suitable for the industrial products.

#### **■ FEATURES**

● Low supply current ...... LL Version

Completely static ...... No clock required

Supply voltage ...... 1.8V to 3.0V

3-state output with wired-OR capability

Non-volatile storage with back-up batteries

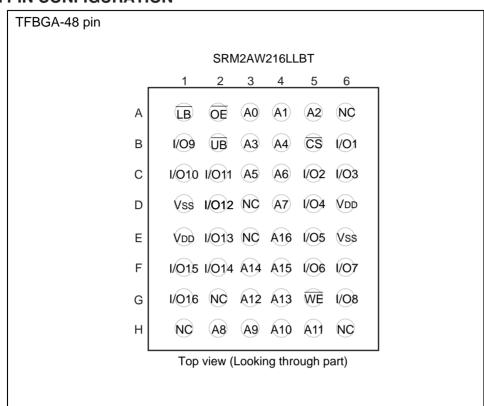

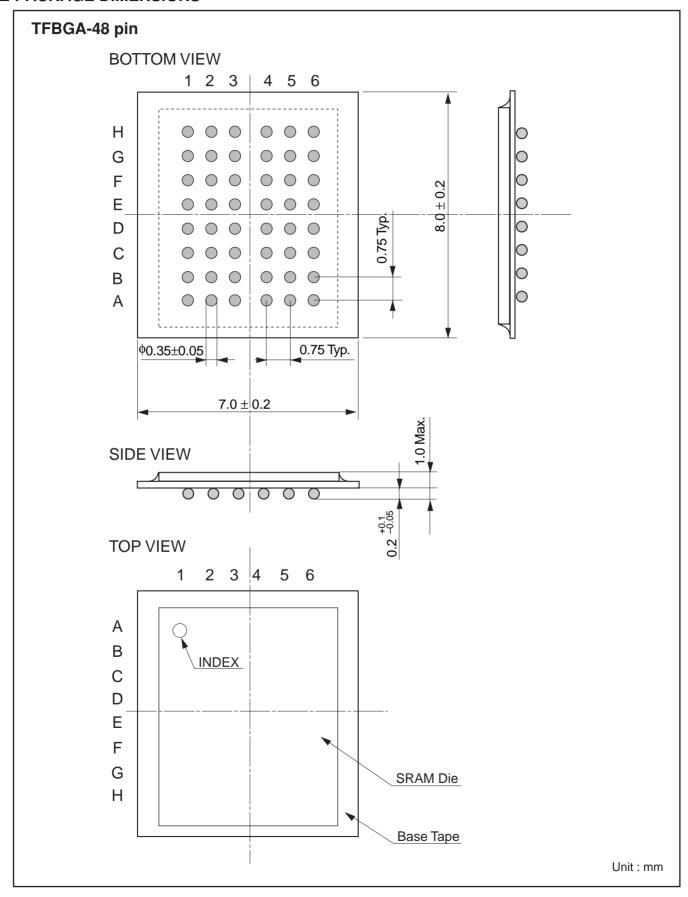

● Package ...... SRM2AW216LLBT TFBGA-48 pin (Tape CSP)

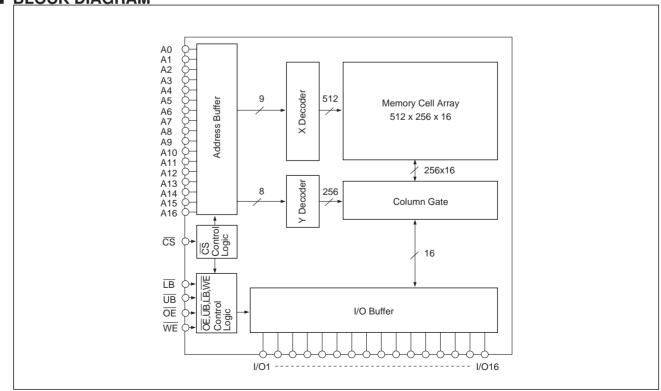

## **■ BLOCK DIAGRAM**

## **■ PIN CONFIGURATION**

## **■ PIN DESCRIPTION**

| A0 to A16  | Address Input               |

|------------|-----------------------------|

| WE         | Write Enable                |

| ŌĒ         | Output Enable               |

| CS         | Chip Select                 |

| LB         | LOWER Byte Enable           |

| ŪB         | UPPER Byte Enable           |

| I/O1 to 16 | Data I/O                    |

| Vdd        | Power Supply (1.8V to 3.0V) |

| Vss        | Power Supply (0V)           |

| NC         | No connection               |

## ■ ABSOLUTE MAXIMUM RATINGS

$(V_{SS}=0V)$

|                                |                  |                                  | ( \$55-0 ) |

|--------------------------------|------------------|----------------------------------|------------|

| Parameter                      | Symbol           | Ratings                          | Unit       |

| Supply voltage                 | $V_{DD}$         | - 0.5 to 3.6                     | V          |

| Input voltage                  | VI               | – 0.5 * to V <sub>DD</sub> + 0.3 | V          |

| Input/Output voltage           | V <sub>I/O</sub> | $-0.5$ * to $V_{DD} + 0.3$       | V          |

| Power dissipation              | P <sub>D</sub>   | 0.5                              | W          |

| Operating temperature          | T <sub>opr</sub> | – 40 to 85                       | °C         |

| Storage temperature            | T <sub>stg</sub> | - 65 to 150                      | °C         |

| Soldering temperature and time | T <sub>sol</sub> | 260°C, 10s (at lead)             | _          |

$<sup>^*</sup>$  V<sub>I</sub>,V<sub>I/O</sub> (Min.) = -2.0V (when pulse width is less than 50ns)

## ■ DC RECOMMENDED OPERATING CONDITIONS

$(Ta = -40 \text{ to } 85 ^{\circ}C)$

| Parameter      | Symbol          | V <sub>D</sub>      | D = 1.8  to  2. | 2V                   | V <sub>DC</sub>     | Unit |                      |       |  |

|----------------|-----------------|---------------------|-----------------|----------------------|---------------------|------|----------------------|-------|--|

| i alametei     | Symbol          | Min.                | Тур.            | Max.                 | Min.                | Тур. | Max.                 | Oille |  |

| Supply voltage | $V_{DD}$        | 1.8                 | 2.0             | 2.2                  | 2.2                 | 2.5  | 3.0                  | V     |  |

|                | V <sub>SS</sub> | 0.0                 | 0.0             | 0.0                  | 0.0                 | 0.0  | 0.0                  | V     |  |

| Input voltage  | V <sub>IH</sub> | 0.75V <sub>DD</sub> | _               | V <sub>DD</sub> +0.3 | 0.75V <sub>DD</sub> | _    | V <sub>DD</sub> +0.3 | V     |  |

| Input voltege  | $V_{IL}$        | - 0.3 <sup>*</sup>  | _               | 0.3                  | - 0.3 <sup>*</sup>  | _    | 0.3                  | V     |  |

<sup>\*</sup> if pulse width is less than 50ns it is - 2.0V

## **■ ELECTRICAL CHARACTERISTICS**

## DC Electrical Characteristics

$(V_{SS} = 0V, Ta = -40 \text{ to } 85 ^{\circ}C)$

| _                               |                   |                                                                                                                                                              |    |              | V <sub>DD</sub> =    | 1.8 to  | 2.2V | $V_{DD} = 2.2 \text{ to } 3.0 \text{V}$ |        |      |      |

|---------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------|----------------------|---------|------|-----------------------------------------|--------|------|------|

| Parameter                       | Symbol            | Conditions                                                                                                                                                   |    |              |                      | Typ. *1 | Max. | Min.                                    | Typ.*2 | Max. | Unit |

| Input leakage current           | ILI               | $V_I = 0$ to $V$                                                                                                                                             | DD |              | -1.0                 | -       | 1.0  | -1.0                                    | 1      | 1.0  | μΑ   |

| Output leakage current          | I <sub>LO</sub>   | $\overline{LB}$ and $\overline{UB} = V_{IH}$ or $\overline{CS} = V_{IH}$ or $\overline{WE} = V_{IL}$ or $\overline{OE} = V_{IH}$ , $V_{I/O} = 0$ to $V_{DD}$ |    |              |                      | -       | 1.0  | -1.0                                    | ı      | 1.0  | μА   |

| High level output voltage       | V <sub>OH</sub>   | VDD≥2.2V, I <sub>OH</sub> = -0.5r                                                                                                                            | nΑ |              | _                    | _       | ı    | 1.8                                     | -      | ı    | V    |

| Tiigit level output voltage     | VOH               | $I_{OH} = -100 \mu A$                                                                                                                                        |    |              | V <sub>DD</sub> -0.2 | -       | ı    | V <sub>DD</sub> -0.2                    | -      | ı    |      |

| Law law law at a stant walte as |                   | $VDD \ge 2.2V$ , $I_{OL} = 0.5m$                                                                                                                             | Α  |              | _                    | _       | -    | _                                       | -      | 0.4  | V    |

| Low level output voltage        | V <sub>OL</sub>   | $I_{OL} = 100\mu A$                                                                                                                                          |    |              | -                    | -       | 0.2  | _                                       | -      | 0.2  | V    |

|                                 | I <sub>DDS</sub>  | CS = V <sub>IH</sub>                                                                                                                                         |    |              | _                    | -       | 0.8  | _                                       | ı      | 1.0  | mA   |

|                                 |                   |                                                                                                                                                              |    | -40 to 85 °C | _                    | _       | 15   | _                                       | -      | 20   |      |

| Standby supply current          |                   | $\overline{\text{CS}} \ge V_{\text{DD}} - 0.2V$                                                                                                              | LL | -40 to 70 °C | _                    | _       | 10   | _                                       | _      | 13.5 | μΑ   |

|                                 | I <sub>DDS1</sub> |                                                                                                                                                              |    | -40 to 40 °C |                      | _       | 3.0  | _                                       | _      | 4.0  |      |

|                                 |                   |                                                                                                                                                              |    | 25 °C        | _                    | 0.15    | 1.5  | _                                       | 0.2    | 2.0  |      |

| Average operating current       | I <sub>DDA</sub>  | $V_I = V_{IL} \text{ or } V_{IH}$ $I_{I/O} = 0\text{mA}, \text{ tcyc} = \text{Min}.$                                                                         |    |              | _                    | 20      | 30   | _                                       | 25     | 35   | mA   |

| Operating Supply Current        | I <sub>DDA1</sub> | $V_I = V_{IL} \text{ or } V_{IH}$<br>$I_{I/O} = 0\text{mA}, \text{ tcyc} = 1\mu\text{s}$                                                                     |    | _            | 2.5                  | 4       | _    | 3                                       | 5      | mA   |      |

|                                 | I <sub>DDO</sub>  | $V_I = V_{IL}$ or $I_{I/O} = 0$ m                                                                                                                            |    | 1            | _                    | 2.5     | 4    | _                                       | 3      | 5    | mA   |

<sup>\*1 :</sup> Typical values are measured at Ta = 25°C and Vpp = 2.0V \*2 : Typical values are measured at Ta = 25°C and Vpp = 2.5V

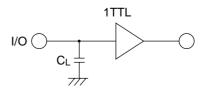

## ● Terminal Capacitance

$(Ta = 25^{\circ}C, f = 1MHz)$

| Parameter           | Symbol           | Conditions     | Min. | Тур. | Max. | Unit |

|---------------------|------------------|----------------|------|------|------|------|

| Address Capacitance | C <sub>ADD</sub> | $V_{ADD} = 0V$ | _    | _    | 8    | pF   |

| Input Capacitance   | Cı               | $V_I = 0V$     | _    | _    | 8    | pF   |

| I/O Capacitance     | C <sub>I/O</sub> | $V_{I/O} = 0V$ | _    | _    | 10   | pF   |

#### AC Electrical Characteristics

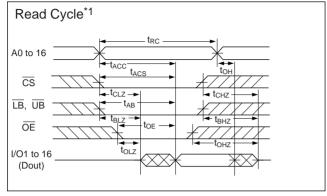

## O Read Cycle

$(V_{SS} = 0V, Ta = -40 \text{ to } 85^{\circ}C)$

|                        |                  | _                  | SRM2AW | 216LLBT1 | SRM2AW | /216LLBT7 |    |

|------------------------|------------------|--------------------|--------|----------|--------|-----------|----|

| Parameter              | Symbol           | Test<br>Conditions | 1.8 to | 2.2V     | 2.2 to | Unit      |    |

|                        |                  | Corrainorio        | Min.   | Max.     | Min.   | Max.      |    |

| Read cycle time        | t <sub>RC</sub>  | 1                  | 100    | _        | 70     | _         | ns |

| Address access time    | t <sub>ACC</sub> | 1                  | _      | 100      | _      | 70        | ns |

| CS access time         | t <sub>ACS</sub> | 1                  | _      | 100      | _      | 70        | ns |

| OE access time         | t <sub>OE</sub>  | 1                  | _      | 60       | _      | 40        | ns |

| LB, UB access time     | t <sub>AB</sub>  | 1                  | _      | 60       | _      | 40        | ns |

| CS output set time     | t <sub>CLZ</sub> | 2                  | 5      | _        | 5      | _         | ns |

| CS output floating     | t <sub>CHZ</sub> | 2                  | _      | 40       | _      | 30        | ns |

| LB, UB output set time | t <sub>BLZ</sub> | 2                  | 0      | _        | 0      | _         | ns |

| LB, UB output floating | t <sub>BHZ</sub> | 2                  | _      | 40       | _      | 30        | ns |

| OE output set time     | t <sub>OLZ</sub> | 2                  | 0      | _        | 0      | _         | ns |

| OE output floating     | t <sub>OHZ</sub> | 2                  | _      | 40       | _      | 30        | ns |

| Output hold time       | t <sub>OH</sub>  | 1                  | 10     | _        | 5      | _         | ns |

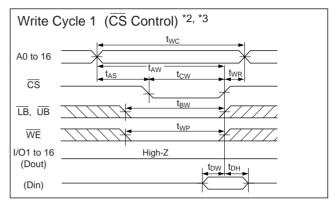

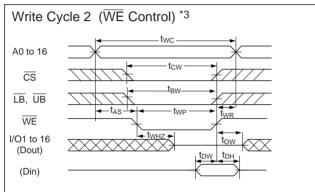

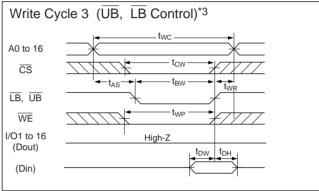

## O Write Cycle

$(V_{SS} = 0V, Ta = -40 \text{ to } 85^{\circ}C)$

|                       |                  |            | SRM2AW | 216LLBT1 | SRM2AW | 216LLBT7 |    |

|-----------------------|------------------|------------|--------|----------|--------|----------|----|

| Parameter             | Symbol           | Test       | 1.8 to | 2.2V     | 2.2 to | Unit     |    |

| T dramotor            | Cymbo.           | Conditions | Min.   | Max.     | Min.   | Max.     |    |

| Write cycle time      | t <sub>WC</sub>  | 1          | 100    | _        | 70     | _        | ns |

| Chip select time (CS) | t <sub>CW</sub>  | 1          | 85     | _        | 60     | _        | ns |

| Address enable time   | t <sub>AW</sub>  | 1          | 85     | _        | 60     | _        | ns |

| Address setup time    | t <sub>AS</sub>  | 1          | 0      | _        | 0      | _        | ns |

| Write pulse width     | t <sub>WP</sub>  | 1          | 80     | _        | 55     | _        | ns |

| LB, UB select time    | t <sub>BW</sub>  | 1          | 85     | _        | 60     | _        | ns |

| Address hold time     | t <sub>WR</sub>  | 1          | 0      | _        | 0      | _        | ns |

| Data setup time       | t <sub>DW</sub>  | 1          | 50     | _        | 35     | _        | ns |

| Data hold time        | t <sub>DH</sub>  | 1          | 0      | _        | 0      | _        | ns |

| WE output floating    | t <sub>WHZ</sub> | 2          | _      | 40       | _      | 30       | ns |

| WE output set time    | t <sub>OW</sub>  | 2          | 5      | _        | 5      | _        | ns |

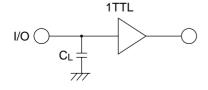

- \*1 Test Conditions

- 1. Input pulse level: 0.3V to 0.8Vpp(1.8V to 3.0V)

- 2.  $t_r = t_f = 5ns$

- 3. Input and output timing reference levels :1/2VDD(1.8V to 3.0V)

- 4. Output load : CL =50pF (Includes Jig Capacitance)

- \*2 Test Conditions

- 1. Input pulse level: 0.3V to 0.8Vpp(1.8V to 3.0V)

- 2.  $t_r = t_f = 5 ns$

- 3. Input timing reference levels :1/2VDD(1.8V to 3.0V)

- 4. Output timing reference levels: ±200mV (The level changed from stable output voltage level)

- 5. Output load :CL = 5pF (Includes Jig Capacitance)

## Timing Chart

- Note: \*1 During read cycle time, WE is to be "High" level.

- \*2 In write cycle time that is controlled by  $\overline{CS}$ , output buffer is to be "Hi-Z" state even if  $\overline{OE}$  is "Low" level.

- \*3 When output buffer is in output state, be careful that do not input the opposite signals to the output data.

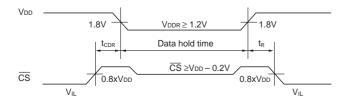

## • DATA RETENTION CHARACTERISTIC WITH LOW VOLTAGE POWER SUPPLY

$(Vss = 0V, Ta = -40 \text{ to } 85^{\circ}C)$

| Parameter                     | Symbol           | Conditions                               | Min. | Typ.*       | Max. | Unit |     |    |

|-------------------------------|------------------|------------------------------------------|------|-------------|------|------|-----|----|

| Data retention supply voltage | $V_{DDR}$        |                                          |      |             |      |      |     | V  |

|                               |                  |                                          |      | -40 to 85°C | _    | _    | 17  |    |

|                               |                  | $V_{DDR} = 2.5V$                         | ١    | –40 to 70°C | _    | -    | 12  |    |

| Data retention curren         | I <sub>DDR</sub> | $\overline{\text{CS}} \ge V_{DD} - 0.2V$ | LL   | -40 to 40°C | _    | -    | 3.5 | μΑ |

|                               |                  | 00 = 1 BB 0:21                           |      | +25°C       | _    | 0.2  | 1.8 |    |

| Data hold time                | t <sub>CDR</sub> |                                          |      |             | 0    | _    | _   | ns |

| Operation recovery time       | t <sub>R</sub>   |                                          |      |             | 5    | _    | _   | ms |

<sup>\*:</sup> Reference data at Ta = 25°C

#### Data retention timing (CS Control)

#### **■ FUNCTIONS**

#### Truth Table

| CS | LB | ŪB | ŌĒ | WE | I/O1 to 8 | I/O9 to 16 | MODE             | I <sub>DD</sub>                      |

|----|----|----|----|----|-----------|------------|------------------|--------------------------------------|

| Н  | Х  | X  | Χ  | Х  | High-Z    | High-Z     | Not Selected     | I <sub>DDS</sub> , I <sub>DDS1</sub> |

| L  | Н  | Н  | Χ  | Х  | High-Z    | High-Z     | Output disable   | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | L  | Н  | Х  | L  | Data In   | High-Z     | Lower Byte Write | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | Н  | L  | Х  | L  | High-Z    | Data In    | Upper Byte Write | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | L  | L  | Х  | L  | Data In   | Data In    | All Byte Write   | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | L  | Н  | L  | Н  | DataOut   | High-Z     | Lower Byte Read  | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | Н  | L  | L  | Н  | High-Z    | DataOut    | Upper Byte Read  | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | L  | L  | L  | Н  | Data Out  | Data Out   | All Byte Read    | I <sub>DDA</sub> , I <sub>DDA1</sub> |

| L  | Х  | Х  | Η  | Н  | High-Z    | High-Z     | Output disable   | I <sub>DDA</sub> , I <sub>DDA1</sub> |

X : High or Low

## Reading data

It is possible to control the data width by  $\overline{LB}$  and  $\overline{UB}$  pins.

(1) Reading data from lower byte

Data is able to be read when the address is set while holding  $\overline{CS}$  ="Low",  $\overline{OE}$ = "Low",  $\overline{LB}$  ="Low" and  $\overline{WE}$  = "High".

(2) Reading data from upper byte

Data is able to be read when the address is set while holding  $\overline{CS}$  = "Low",  $\overline{OE}$  = "Low",  $\overline{UB}$  = "Low" and  $\overline{WE}$  = "High".

(3) Reading data from both bytes

Data is able to be read when the address is set while holding  $\overline{CS}$  = "Low",  $\overline{OE}$  ="Low",  $\overline{UB}$  ="Low",  $\overline{LB}$  = "Low", and  $\overline{WE}$  = "High"

Since I/O pins are in "Hi-Z" state when  $\overline{OE}$  = "High", the data bus line can be used for any other objective, then access time is apparently able to be cut down.

#### Writing data

(1) Writing data into lower byte

There are the following three ways of writing data into memory.

- i) Hold WE = "Low", UB = "High" and LB = "Low", set address and give "Low" pulse to CS.

- ii) Hold  $\overline{CS}$  = "Low",  $\overline{UB}$  = "High" and  $\overline{LB}$  = "Low", set address and give "Low" pulse to  $\overline{WE}$ .

- iii) Hold  $\overline{WE}$ ="Low",  $\overline{CS}$ ="Low" and  $\overline{UB}$  = "High", set address and give "Low" pulse to  $\overline{LB}$ .

Anyway, data on I/O pins are latched up into the memory cell during  $\overline{CS}$  ="Low", WE ="Low", and LB = "Low".

(2) Writing data into upper byte

There are the following three ways of writing data into the memory.

- i) Hold  $\overline{WE}$  = "Low",  $\overline{LB}$  = "High" and  $\overline{UB}$  = "Low", set address and give "Low" pulse to  $\overline{CS}$ .

- ii) Hold CS = "Low", LB = "High" and UB = "Low", set address and give "Low" pulse to WE.

- iii) Hold WE="Low", CS="Low" and LB = "High", set address and give "Low" pulse to UB.

Anyway, data on I/O pins are latched up into the memory cell during CS = "Low", WE = "Low", and  $\overline{UB}$  = "Low". (3)Writing data into both bytes

There are the following three ways of writing data into the memory.

- i) Hold  $\overline{WE}$  = "Low",  $\overline{LB}$  and  $\overline{UB}$  = "Low", set address and give "Low" pulse to  $\overline{CS}$ .

- ii) Hold CS = "Low", LB and UB = "Low", set address and give "Low" pulse to WE.

- iii) Hold WE="Low" and CS="Low", set address and give "Low" pulse to LB and UB.

Anyway, data on I/O pins are latched up into the memory cell during  $\overline{CS}$  = "Low",  $\overline{WE}$  = "Low",  $\overline{UB}$  and  $\overline{LB}$  = "Low".

As DATA I/O pins are in "Hi-Z" when  $\overline{CS}$ ="High",  $\overline{OE}$ ="High", or  $\overline{LB}$  and  $\overline{UB}$ ="High", the contention on the data bus can be avoided. But while I/O pins are in the output state, the data that is opposite to the output data should not be given.

## Standby mode

When  $\overline{CS}$  is "High", the chip is in the <u>standby mode (only retaining data operation)</u>. In <u>this case data I/O pins</u> are Hi-Z, and all inputs of addresses,  $\overline{WE}$ ,  $\overline{OE}$ ,  $\overline{UB}$ ,  $\overline{LB}$ , and data are inhibited. When  $\overline{CS}$  is in the range over VDD–0.2V, there is almost no current flow except through the high resistance parts of the memory.

## Data retention at low voltage

In case of the data retention in the stadby mode, the power supply can be gone down till the specified voltage. But it is impossible to write or read in this mode.

## ■ PACKAGE DIMENSIONS

## **■ CHARACTERISTICS CURVES**

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 1999 All right reserved.

#### **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICES MARKETING DIVISION

IC Marketing & Engineering Group

ED International Marketing Department I (Europe & U.S.A.)

421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5812 FAX: 042-587-5564

**ED International Marketing Department II (Asia)** 421-8, Hino, Hino-shi, Tokyo 191-8501, JAPAN Phone: 042-587-5814 FAX: 042-587-5110

■ EPSON Electronic Devices Website http://www.epson.co.jp/device/

Revised October,1999 Printed in Japan (\$\structure{S}\)

Rev.1.3